The computing realm is evolving rapidly, as always.

Artificial intelligence (AI) and high-performance computing (HPC) workloads in data centres are poised to get a significant boost with Samsung’s cool new kit.

Check out Samsung’s brand new and industry’s first DRAM-based memory module, which supports the new CXL interconnect standard.

With Samsung’s DDR5 technology, the CXL-incorporated PCIe 5.0 module comes in the EDSFF form factor, allowing server systems to significantly scale memory capacity and bandwidth, enhancing AI and HPC applications, as well as cloud environments.

But hey – we know you’re probably thinking: “OMG! All this jargon is making my head spin!”

Hang in there, full explanation follows!

Elevating data centre performance.

Fueling the trend toward heterogeneous computing, the rise of big data and AI have been pushing the boundaries of hardware performance, where multiple processors work in parallel to process massive deluges of data.

The integration of CXL into the memory module – created to overcome many of the technical limitations of PCIe – is especially suited for data centre usage, where multiple bandwidth-hungry devices and vast shared memory pools are commonplace.

Unlike traditional DDR-based memory with limited memory channels, Samsung’s new acronym-loaded module has the ability to scale memory capacity to the terabyte level, while substantially decreasing system latency caused by memory caching.

A resulting high-speed, low latency communication between the host processor and devices such as accelerators, memory buffers and smart input/output (I/O) devices is enabled, while expanding memory capacity and bandwidth well beyond current technology.

The CXL hardware innovation is not the only aspect that stands out – Samsung has added a couple of other goodies to their new kit as well.

Controller and software technologies such as memory mapping, interface converting and error management were thrown in too. This will allow CPUs or GPUs to recognise the CXL-based memory and utilise it as the main memory.

In their announcement, Samsung quoted Intel and AMD, hinting which partners they are working with.

They also revealed that their new tech has been successfully validated on Intel’s next-gen server platforms, signalling the beginning of a new era in CXL-based memory using the latest DDR5 standard.

Now, with all these updates in mind, let’s dive into all these acronyms that the IT industry is so fond of!

Acronyms galore.

DRAM (Dynamic Random Access Memory) – Widely used as a computer’s main memory. Each DRAM memory cell consists of a transistor and a capacitor within an integrated circuit, and a data bit is stored in the capacitor.

DDR5 (Double Data Rate 5) – A specification of DRAM modules. The latest DDR5 standard was released in 2020, with lower power consumption while doubling the bandwidth of its predecessor – DDR4. A neat comparison between different DDR versions can be seen here.

PCIe 5.0 (Peripheral Component Interconnect Express) – Primarily used as a standardised interface for motherboard components including memory, graphics and storage.

CXL (Compute Express Link) – An open interconnect technology for enabling efficient, coherent memory accesses between a host, such as a CPU, and a device, such as a hardware accelerator, that is handling intensive workloads – machine learning (ML), AI or HPC applications.

EDSFF (Enterprise & Data Centre SSD Form Factor) – A new storage form factor aimed to overcome the challenges of existing interfaces in data centres. The data centre system-optimised design strives to meet customer needs for storage devices having high density, capacity and performance options.

Hopefully we’ve got you covered!

We are extremely excited to see the innovation Samsung’s new tech will bring to the table once it’s rolled out to data centres and cloud providers.

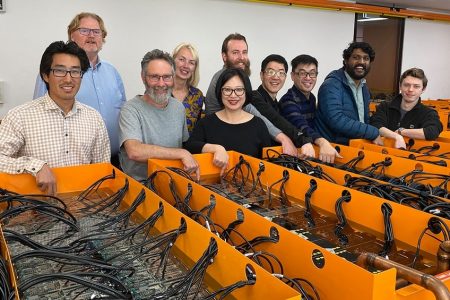

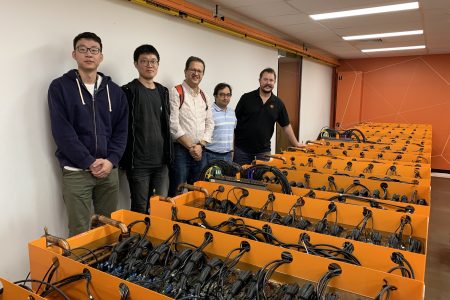

Main picture: Industry’s first DRAM-based memory solution that runs on the CXL interface. Photo credits: Business Wire